Тема: Логический элемент "равно"

Добрый день, коллеги!

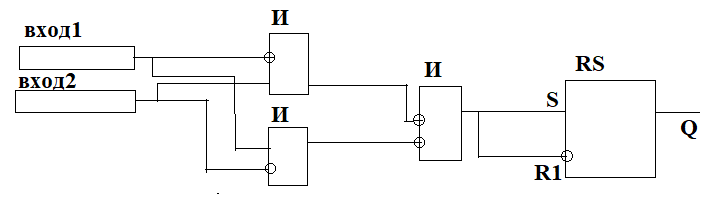

Возникла такая задача, заменить логический блок "равно" с помощью двух блоков "RS-триггер". Более подробно: то есть у нас есть две булевые переменные (0 или 1) и нужно, чтобы триггеры в сумме (блок логическое "И", возможно "ИЛИ") на выходе давали 1(TRUE) если две переменные равны (то есть или два нуля или две единицы), а если переменные разные (01 10) то на выходе выдавало 0 (FALSE).

Возможно кто то уже сталкивался с подобным?

P.S. написал сообщение в этом разделе, потому что не нашел что то более подходящего под этот вопрос.